關鍵詞 |

上海信號完整性檢測,信號完整性檢測 |

面向地區 |

通過電磁仿真與去嵌入技術,解析芯片封裝引線電感、寄生電容對高速信號的影響,指導BGA封裝設計與信號引腳分配,降低高速SerDes鏈路的信號完整性風險。

通過統計眼圖與誤碼浴盆曲線分析,量化工藝偏差、溫度漂移與老化因素對鏈路裕量的影響,制定汽車電子ASIL-D等級的安全冗余策略。

通過諧振腔法或傳輸線法測量PCB基材的介電常數(Dk)與損耗因子(Df),為112Gbps以上高速鏈路提供材料選型依據,降低介質損耗對信號衰減的影響。

部署基于云平臺的分布式電磁仿真引擎,加速多工況、多參數組合的高速鏈路優化迭代,支撐復雜系統級SI/PI協同設計需求。

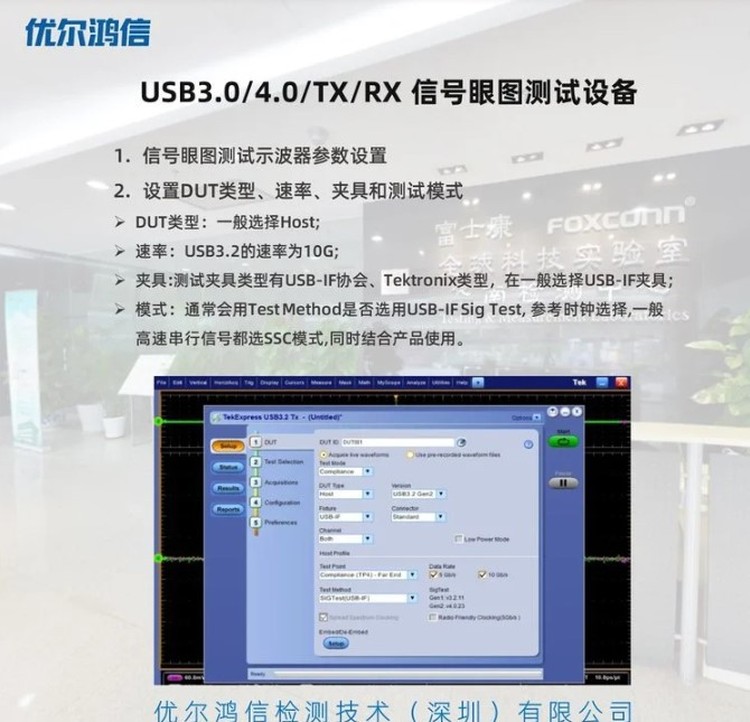

針對高速傳輸線的阻抗匹配需求,通過時域反射(TDR)技術分析路徑阻抗變化,定位PCB走線、連接器或過孔處的阻抗突變點,降低信號反射與失真風險,適用于PCIe/USB等高速接口設計驗證。

驗證SerDes芯片在PAM4/NRZ調制下的串行化與解串性能,優化時鐘數據恢復(CDR)電路參數,滿足AI訓練芯片間互連的吞吐量需求。

廣州本地信號完整性檢測熱銷信息