關鍵詞 |

上海信號完整性檢測,信號完整性檢測 |

面向地區 |

通過電磁仿真與去嵌入技術,解析芯片封裝引線電感、寄生電容對高速信號的影響,指導BGA封裝設計與信號引腳分配,降低高速SerDes鏈路的信號完整性風險。

量化時鐘源至接收端的抖動傳遞函數(JTF),識別PLL、時鐘樹及電源噪聲對系統抖動的貢獻,優化時鐘架構設計,滿足JEDEC標準對DDR5內存時序精度的嚴苛要求。

針對硅光芯片的電光轉換接口,測試高速電信號與光調制器的匹配特性,優化行波電極設計與阻抗匹配網絡,降低800G光引擎的功耗與誤碼率。

集成SPICE電路模型與電磁場仿真工具,分析高速信號對電源網絡的噪聲耦合路徑,優化電源分割與跨分割信號的回流設計,降低混合信號系統的串擾風險。

集成可編程阻抗匹配電路,實時校準因溫度、老化引起的傳輸線阻抗漂移,確保自動駕駛車載攝像頭鏈路在寬溫范圍內的穩定性。

驗證SerDes芯片在PAM4/NRZ調制下的串行化與解串性能,優化時鐘數據恢復(CDR)電路參數,滿足AI訓練芯片間互連的吞吐量需求。

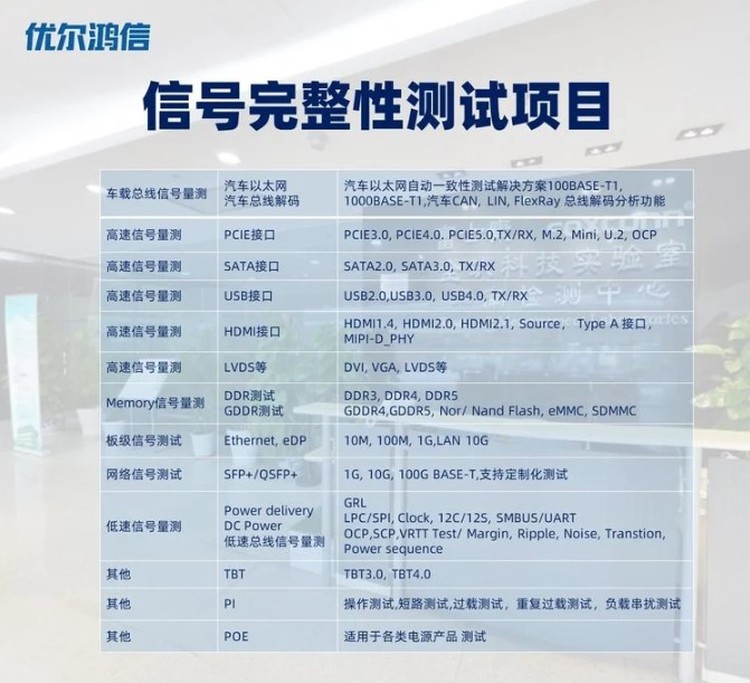

優爾鴻信檢測隸屬于富士康集團,成立于1996年,一直深耕于檢測行業,目前擁有4000+的各類檢測設備,2000+以上的檢測人員。在昆山、煙臺、武漢、成都、重慶等均設有分支機構。設有:量測實驗室、噪音檢測實驗室、模擬機械實驗室、可靠性檢測實驗室、材料檢測實驗室、元素檢測實驗室等各大實驗室!

廣州本地信號完整性檢測熱銷信息